Export Citatio

# Tuning the interlayer microstructure and residual stress of buffer-free direct bonding GaN/Si heterostructures

Cite as: Appl. Phys. Lett. **122**, 082103 (2023); doi: 10.1063/5.0135138 Submitted: 16 November 2022 · Accepted: 30 January 2023 · Published Online: 21 February 2023

Yan Zhou,<sup>1,2,a)</sup> (D Shi Zhou,<sup>2,3</sup> Shun Wan,<sup>4,a)</sup> Bo Zou,<sup>5</sup> Yuxia Feng,<sup>6</sup> (D Rui Mei,<sup>2</sup> Heng Wu,<sup>2</sup> (D Naoteru Shigekawa,<sup>7,8</sup> (D Jianbo Liang,<sup>7,8,a)</sup> Pingheng Tan,<sup>2</sup> (D and Martin Kuball<sup>1,a)</sup> (D

# AFFILIATIONS

<sup>1</sup>Center for Device Thermography and Reliability (CDTR), H. H. Wills Physics Laboratory, University of Bristol, Tyndall Avenue, Bristol BS8 1TL, United Kingdom

<sup>2</sup>State Key Laboratory of Superlattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China

<sup>3</sup>Nano Science and Technology Institute, University of Science and Technology of China, Hefei 230026, China

<sup>4</sup>Center for High Pressure Science and Technology of Advanced Research, Shanghai 201203, China

<sup>5</sup>School of Science, Harbin Institute of Technology, Shenzhen 518055, China

<sup>6</sup>Key Laboratory of Optoelectronics Technology, Ministry of Education, Beijing University of Technology, Beijing 100124, China <sup>7</sup>Department of Electronic Information Systems, Osaka City University, Sugimoto 3-3-138, Sumiyoshi, Osaka 558-8585, Japan <sup>8</sup>Graduate School of Engineering, Osaka Metropolitan University, Sugimoto 3-3-138, Sumiyoshi, Osaka 558-8585, Japan

<sup>a)</sup>Authors to whom correspondence should be addressed: yan.zhou@bristol.ac.uk; shun.wan@hpstar.ac.cn; liang@omu.ac.jp; and martin.kuball@bristol.ac.uk

### ABSTRACT

The direct integration of GaN with Si can boost great potential for low-cost, large-scale, and high-power device applications. However, it is still challengeable to directly grow GaN on Si without using thick strain relief buffer layers due to their large lattice and thermal-expansion-coefficient mismatches. In this work, a GaN/Si heterointerface without any buffer layer is fabricated at room temperature via surface activated bonding (SAB). The residual stress states and interfacial microstructures of GaN/Si heterostructures were systematically investigated through micro-Raman spectroscopy and transmission electron microscopy. Compared to the large compressive stress that existed in GaN layers grown on Si by metalorganic chemical vapor deposition, a significantly relaxed and uniform small tensile stress was observed in GaN layers bonded to Si by SAB; this is mainly ascribed to the amorphous layer formed at the bonding interface. In addition, the interfacial microstructure and stress states of bonded GaN/Si heterointerfaces was found to be significantly tuned by appropriate thermal annealing. With increasing annealing temperature, the amorphous interlayer formed at the as-bonded interface gradually transforms into a thin crystallized interlayer without any observable defects even after annealing at 1000 °C, while the interlayer stresses at both GaN layer and Si monotonically change due to the interfacial re-crystallization. This work moves an important step forward directly integrating GaN to the present Si CMOS technology with high quality thin interfaces and brings great promises for wafer-scale low-cost fabrication of GaN electronics.

© 2023 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http:// creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0135138

Gallium nitride (GaN) is one of the most important semiconductor materials for the present and future high-power and highfrequency devices,<sup>1–3</sup> mainly due to its superior physical properties of a wide bandgap, a high electron saturation velocity, a high breakdown field, and a high chemical stability.<sup>4–6</sup> Though there are many commercial prospects to use SiC or diamond as substrates for GaN, one of the critical issues GaN-based devices still face is their comparably expensive cost for compatibility with Si-based integrated circuits. Integrating GaN with Si substrates would enable the fabrication of low-cost and multi-functional chips.<sup>7</sup> Although GaN epitaxial layers integrated on Si through crystal growth methods have become a commercial product, thick strain relief layers, such as AlN, AlN/AlGaN,

and AlN/GaN, need to be used because of the large residual stresses induced by their large mismatches in lattice (17% between GaN and Si) and thermal-expansion-coefficient.<sup>8–15</sup> Large residual stresses affect the electrical and optical properties of GaN-based devices.<sup>16,17</sup> In addition, the strategy of growing thick strain relief layers for GaN/Si heterostructures also introduces a large thermal boundary resistance at interfaces, thus degrading the critical thermal management performance of GaN-based devices.<sup>10,18,19</sup>

To realize high quality, low stress GaN/Si heterointerfaces, integrating GaN with Si via wafer bonding has attracted tremendous interest and has achieved great progress through using various buffer layers;20-22 however, the direct bonding of GaN to Si substrates without any buffer layers is still rather challenging though very attractive as it would remove any sizable thermal barrier at the GaN/Si interface. Recently, room-temperature direct bonding of dissimilar materials with a large lattice mismatch between heterostructures, such as diamond/Si, GaN/diamond, and GaN/SiC, via surface-activated-bonding (SAB) exhibited excellent performance and great potential.<sup>21</sup> Despite that a relative thick amorphous interlayer is normally formed at the interface after SAB,<sup>23-26</sup> which can affect the residual stress, interlayer microstructure, and device performance of various heterostructures that is still not fully understood, thermal annealing is known to modulate the defects, modify the amorphous structure, and change the residual stress of heterostructures.<sup>23,24,27,28</sup> Though *in situ* measuring the interlayer microstructure and residual stress during annealing is still a challenge, confocal micro-Raman spectroscopy can provide <sup>24,29–34</sup> The sub-micrometer resolution to reveal the local stress.<sup>2</sup> atomic-scale microstructure of different heterointerfaces after different annealing can be revealed through transmission electron microscopy (TEM).

In this work, the direct bonding of GaN/Si heterostructures without any buffer layers was realized here by SAB at room temperature. The residual stress and the interlayer microstructure along with the annealing impacts of GaN/Si heterostructures were systematically investigated and compared with those of metalorganic chemical vapor deposition (MOCVD) grown GaN/Si heterostructures, using confocal micro-Raman spectroscopy and TEM. This work will provide a perspective for controlling the residual stress and interface quality in GaN/Si or similar heterostructures and for developing novel device structures.

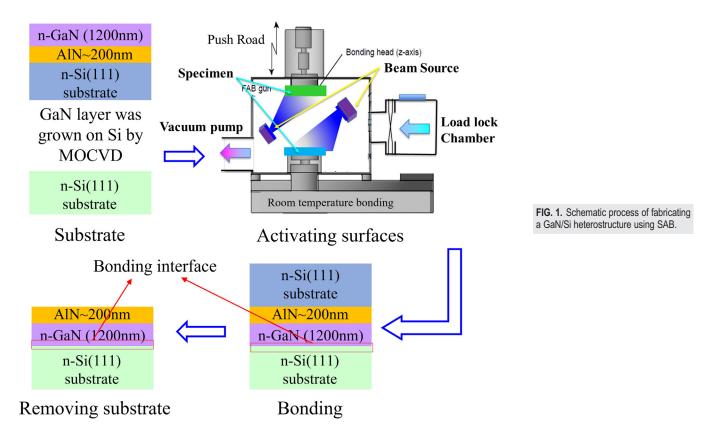

GaN(0001) epitaxial layers used in this study were grown by MOCVD on 4-in. n-Si(111) substrates. To grow the GaN/Si heterostructures, trimethylgallium (TMG), trimethyl aluminum (TMA), and ammonia (NH<sub>3</sub>) were used as sources for Ga, Al, and N, respectively. Prior to grow GaN, the Si substrate was cleaned in H<sub>2</sub> ambient at 1000 °C, followed by the growth of about 200 nm-thick AlN buffer layer at 1060 °C. A 1.2 µm-thick GaN layer was then grown on the AlN buffer layer at 1000 °C. The GaN epitaxial layers grown on Si and an additional target n-Si(111) substrate used for the bonding were cleaned with acetone and ethanol in an ultrasonic bath for 300 s, dried under N2, and then loaded into the SAB chamber. After their surfaces were activated by fast Ar atom beam irradiation,<sup>35,36</sup> the GaN epitaxial layers were bonded to the target n-Si(111) substrates at room temperature under optimized bonding parameters of a vacuum pressure of  $5 \times 10^{-7}$  Pa and an external load of 1 GPa for 60 s, resulting in a Si/GaN/Si heterostructure. After bonding, the grown Si substrate was removed by mechanical polishing and chemical wet-etching. To avoid etching the bonded n-Si(111) substrate, a SiO<sub>2</sub> layer was deposited on the backside of the Si substrate by the RF sputtering. Here, the grown GaN-on-Si is Ga-polar, while the SAB process results in an N-polar GaN-on-Si. The detailed process of GaN/Si heterostructure fabricated by SAB is shown in Fig. 1.

The residual stress in the SAB fabricated GaN/Si heterostructure was investigated systematically by micro-Raman spectroscopy. Raman mapping measurements were confocal on the GaN surface and the interface to the bonded n-Si(111) wafer in an area of  $40 \times 40 \,\mu m^2$ mapped with a step size of  $1 \,\mu m$ . A Renishaw inVia confocal micro-Raman spectroscopy with a measurement configuration of 180° backscattering geometry, an Ar<sup>+</sup> laser of 488 nm, a diffraction grating of 2400 lines/mm, a  $50 \times 0.6$  NA long working distance objective lens, and a laser sport size of  $\sim 1.5 \,\mu m$  was used. Samples were also measured at elevated temperatures by in situ micro-Raman in a hightemperature heating/cooling stage (Linkam TS-1500) with a temperature stability of  $\pm 1$  °C for controlling the sample temperature. The bonded samples were annealed at 400, 700, and 1000 °C for 300 s in N2 gas atmosphere. The GaN and Si Raman mode frequencies were determined by performing a Lorentz fitting to their recorded spectra, with a shift resolution as low as  $\pm 0.02 \text{ cm}^{-1}$  within the measurement time; Raman shift of the Si calibration wafer before and after each measurement was measured to check for stability and accuracy. The  $E_2^{\text{high}}$  mode of GaN was employed to monitor the residual stress in GaN layers because of its higher stress sensitivity.<sup>37</sup> The interfacial microstructures of GaN/Si heterostructure were investigated by TEM (JEM-2200FS).

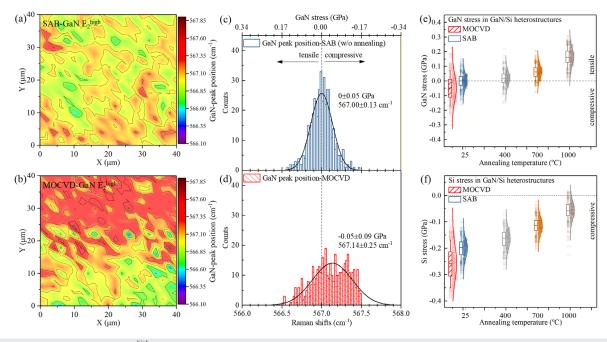

Raman peak positions from mapping the GaN  $E_2^{\text{high}}$  mode in SAB fabricated GaN/Si heterostructures and in the MOCVD as-grown sample prior to SAB are shown in Figs. 2(a) and 2(b); the corresponding histograms of peak positions and stress distributions are displayed in Figs. 2(c) and 2(d). For unstressed GaN, numerous values for Raman peak of GaN  $E_2^{\text{high}}$  mode have been reported in the literature;38here, we measured a 356  $\mu$ m-thick free-standing GaN substrate grown by hydride vapor-phase-epitaxy as a reference stress-free bulk value, determining the Raman peak of GaN  $E_2^{\text{high}}$  at 567 cm<sup>-1</sup>. For the Si  $F_{2g}$  mode in stress-free case, 520 cm<sup>-1</sup> was measured. As shown in Figs. 2(a) and 2(b), the Raman peak of the GaN  $E_2^{\text{high}}$  mode in GaN/Si heterostructures fabricated by SAB and MOCVD was found to range from 566.57 to 567.46 and 566.35 to  $567.87 \text{ cm}^{-1}$ ; their averaged Raman peak positions were determined to be  $567 \pm 0.13$  and  $567.14 \pm 0.25$  cm<sup>-1</sup>, respectively [Figs. 2(c) and 2(d)]. The GaN peak that shifted to higher wave numbers compared to the stress-free bulk value of 567 cm<sup>-1</sup> indicates that the GaN layer grown on Si was under compressive stress. Note that there were some variations in the GaN peak of MOCVD grown GaN/Si heterostructure, indicating that some inhomogeneity existed. According to the literature, the phonon frequencies of GaN  $E_2^{\text{high}}$  mode and Si  $F_{2g}$  mode both shift linearly with stress at a rate of 2.9 and 2.3 cm<sup>-1</sup> GPa<sup>-1</sup>, respectively.<sup>41,42</sup> We used these coefficients to calculate the residual stress values in GaN/Si heterostructures from the Raman peak shifts of GaN and Si with respect to their stress-free bulk values. As demonstrated in Figs. 2(c) and 2(d), a near-zero small tensile residual stress of  $0 \pm 0.05$  GPa with respect to the unstressed bulk value was extracted from the GaN layer of the SAB fabricated GaN/Si heterostructures, implying that the residual stress is significantly relaxed in SAB as-bonded GaN/Si heterostructures, while a compressive stress of  $-0.05 \pm 0.09$  GPa was present in the GaN layer

# **Applied Physics Letters**

scitation.org/journal/apl

of MOCVD grown GaN/Si heterostructures; this is consistent with values reported in the literature for GaN grown on Si (111) by MOCVD using similar strain relief buffer layers.<sup>39,43,44</sup>

Residual stress in SAB fabricated heterostructures was previously found to change with annealing temperature.<sup>23,24</sup> Based on these earlier studies, we explored the effects of thermal annealing on residual stress and interfacial structure of SAB fabricated GaN/Si heterostructures. The averaged residual stresses and corresponding statistic distributions in GaN and Si layers of SAB fabricated GaN/Si heterostructures after annealing at different temperatures are shown in Figs. 2(e) and 2(f), respectively, while those in GaN and Si layers of MOCVD grown GaN/Si heterostructures were also measured at room temperature for comparison in Figs. 2(e) and 2(f). Here, the shown residual stresses represent the averaged value over the area of  $40 \times 40 \ \mu m^2$ . The magnitude of error bars and the nearby statistic curves reflected the range and homogeneity of stress distribution in GaN epilayer and Si substrate. Residual stresses along with their distribution ranges of GaN and Si in SAB fabricated GaN/Si heterostructures prior to annealing were smaller than those of MOCVD grown GaN/Si heterostructures. Moreover, the average residual stresses of GaN and Si change to different levels with increasing annealing temperature at different rates, for example, after annealing at 1000 °C, their residual stresses become a larger tensile (0.16 GPa) and a smaller compressive (0.06 GPa) stress, respectively. However, after annealing below 700 °C, there are negligible changes in the residual stress of GaN, while the compressive stress in Si decreased linearly with increased temperature.

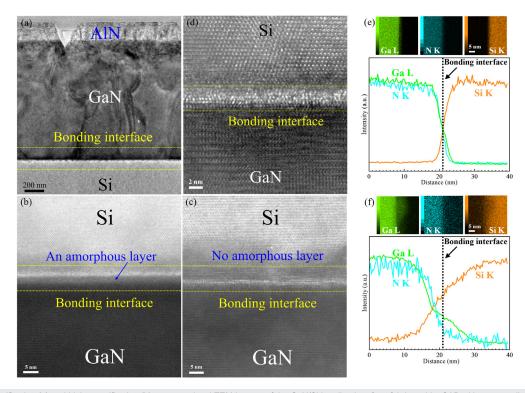

To gain insight into the interfacial microstructure evolution under different annealing temperatures, the local nanoscale and atomic-scale SAB bonded GaN/Si interfaces were examined by TEM. As shown in Figs. 3(a) and 3(d), low and high magnification and high-resolution cross-sectional TEM images of the GaN/Si bonding interface fabricated by SAB without and with annealing at 1000 °C were performed, respectively. It is apparent in Fig. 3(a) that a relatively sharp interface without any micro-voids was observed at the bonding interface, including after removal of the growth substrate. Meanwhile, a disordered amorphous-like interlayer with a thickness of tens of nanometers was present at the unannealed bonding interface [Fig. 3(b)]. After annealing at 1000 °C, no amorphous layer was observed at the bonding interface [Fig. 3(c)]; instead, a crystallized interlayer of only few nanometer thin was formed at the bonding interface [Fig. 3(d)]. More importantly, no structural defects, such as cracks, were observed at the interface whether without or with annealing. Further energydispersive x-ray spectroscopy (EDS) mappings of the un-annealed and bonding interface annealed at 1000 °C show that the crystallized interlayer is composed of Ga, N, and Si elements [Figs. 3(e) and 3(f)]. We also note that after annealing at 1000 °C, the intensity gradients of Ga, N, and Si show Si atoms diffused into the GaN side, and Ga and N atoms diffused into the Si adjacent to the bonding interface due to the thermal annealing effects.

Relaxation of residual stress that occurred in the GaN layer of SAB fabricated GaN/Si heterostructure should be attributed to the formation of an amorphous layer at the bonding interface. Although a

FIG. 2. Raman peak position maps of  $E_2^{high}$  mode of GaN layer in (a) GaN/Si heterostructures fabricated by SAB and (b) MOCVD as-grown sample on Si substrate. Histogram statistic distributions for Raman peak positions and the residual stresses of GaN in the corresponding structures extracted from their Raman data are shown in (c) and (d), respectively; a Raman peak of 567 cm<sup>-1</sup> is taken for unstressed GaN as the reference value, while 2.9 cm<sup>-1</sup>/GPa is taken for its stress coefficient. Red and blue colors represent MOCVD and SAB samples, respectively. Residual stresses of GaN (e) and Si (f) in SAB fabricated GaN/Si heterostructures, averaged over an area of 40 × 40  $\mu$ m<sup>2</sup>, after annealing at different temperatures. Error bars represent the standard deviation of the average value and reflect the level of homogeneousness of residual stress.

similar amorphous layer was also observed at the SAB fabricated Si/SiC, Si/GaAs, Si/diamond interfaces, 23, 25, 45, 46 this amorphous layer plays a cushioning effect across the GaN/Si bonding interface, which can relax the residual stress caused by the large difference in the lattice constant between Si and GaN (~17%). The formation of the amorphous layer at the bonding interface is because of the fast Ar atom beam activation during the bonding process. It was found that the residual stress in SAB bonded GaN/Si heterostructure strongly depended on the post-annealing temperature. Also, no sizable amorphous layer was observed at the bonding interface after annealing at 1000 °C; moreover, the TEM images (Fig. 3) illustrate that the amorphous layer recrystallized after annealing at high temperature. The residual stress in GaN of SAB fabricated GaN/Si heterostructures increased with increasing annealing temperature, which should be correlated with the decrease in the amorphous layer thickness, making it more and more difficult to ease up the residual stress caused by lattice and thermal-expansion mismatches between GaN and Si. Because the lattice constant of GaN is smaller than that of Si (111) and its thermalexpansion-coefficient is larger than those of Si and the amorphous layer, tensile stress becomes more significant in the GaN layers with increasing annealing temperature. However, the compressive stress in Si near the bonding interface decreased with increasing annealing temperature.

It has been reported that a silicon nitride layer can form at the GaN/Si interface due to the direct reaction of nitride with silicon.<sup>47</sup> We are then led to the hypothesis that a compressive stress could exist in the interlayer if the silicon nitride layer was to be formed at the GaN/Si bonding interface. Because there is a large residual stress

difference between GaN and Si layers near the bonding interface after annealing at 1000  $^{\circ}$ C, a compressive stress likely exists in the recrystallized interlayer to compensate the reduction in compressive stress in Si. Moreover, we note that no structural defects were observed at the bonding interface. These advantages indicated that it is possible to obtain stress-free GaN epitaxial layers through SAB technique at room temperature and tune the interlayer structure and residual stress through appropriate temperature annealing.

In conclusion, GaN epitaxial wafers were directly bonded to Si(111) substrates by SAB without any buffer at room temperature. The residual stress and interlayer microstructure in SAB bonded GaN/ Si heterostructure were systematically investigated and compared with those of MOCVD grown GaN/Si heterostructure, using confocal micro-Raman spectroscopy and TEM. It was found that the residual stress was greatly relaxed in SAB fabricated GaN/Si heterostructures and a uniform distribution of small tensile residual stress was obtained; these contrast to a larger compressive stress in MOCVD grown GaN/ Si heterostructures. The main reason was the formation of an amorphous layer at the bonding interface supporting stress relaxation. The interlayer microstructure and residual stress of SAB bonded GaN/Si heterostructures could be significantly tuned by appropriate thermal annealing. Residual stress was observed to monotonically change with increasing temperature, correlating with the evolution of amorphous layer. After annealing at 1000 °C, the amorphous interlayer disappeared, while a few nanometer thin crystallized interlayer formed at the bonding interface, without any observable defects. This work realizes the buffer-free direct bonding of GaN epilayer with Si substrate,

FIG. 3. A low magnification (a) and high magnification (b) cross-sectional TEM images of the GaN/Si bonding interface fabricated by SAB without annealing, as well as a high magnification (c) and high resolution (d) cross-sectional TEM images of the GaN/Si bonding interface fabricated by SAB after annealing at 1000 °C. The EDS mapping of the SAB bonded interface region (e) without annealing and (f) after annealing at 1000 °C.

unveils the tuning potential of GaN/Si interfaces, and provides great prospects for low-cost, large-scale, and multi-functional GaN/Si device applications.

This work was, in part, supported by JSPS KAKENHI under Grant No. JP20K04581, the Osaka City University (OCU) Strategic Research Grant 2020 for top basic research, the National Natural Science Foundation of China under Grant No. 42050203, and China Postdoctoral Science Foundation under Grant No. 2019M663904XB. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of JSPS.

#### AUTHOR DECLARATIONS

# **Conflict of Interest**

The authors have no conflicts to disclose.

#### **Author Contributions**

Yan Zhou, Shi Zhou, Shun Wan contributed equally to this work.

Yan Zhou: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Resources (equal); Writing – original draft (equal); Writing – review & editing (equal). Ping-Heng Tan: Investigation (supporting). Martin Kuball: Conceptualization (equal); Investigation (equal); Project administration (equal); Resources (equal); Supervision (equal); Writing – review & editing (equal). Shi Zhou: Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Writing – original draft (equal); Writing – review & editing (equal). Shun Wan: Data curation (equal); Formal analysis (equal); Funding acquisition (equal); Investigation (equal); Methodology (equal); Writing – review & editing (equal). Bo Zou: Formal analysis (equal); Investigation (equal); Methodology (equal); Writing – review & editing (equal). Bo Zou: Formal analysis (equal); Investigation (equal); Methodology (equal); Writing – review & editing (equal). Yuxia Feng: Investigation (supporting). Rui Mei: Investigation (supporting). Heng Wu: Investigation (supporting). Naoteru Shigekawa: Investigation (equal); Project administration (equal); Resources (equal); Supervision (equal); Writing – review & editing (equal). Jianbo Liang: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Funding acquisition (equal); Investigation (equal); Investigation (equal); Project administration (equal); Project administration (equal); Project administration (equal); Project administration (equal); Investigation (equal); Investigation (equal); Investigation (equal); Investigation (equal); Project administration (equal); Project administration (equal); Project administration (equal); Investigation (equal); Project administration (equal); Writing – review & editing (equal).

# DATA AVAILABILITY

The data that support the findings of this study are available within the article or from the corresponding authors upon reasonable request.

#### REFERENCES

<sup>1</sup>H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P. R. Chalker, M. Charles, K. J. Chen, N. Chowdhury, and R. Chu, J. Phys. D **51**(16), 163001 (2018).

<sup>2</sup>L. Nela, R. V. Erp, G. Kampitsis, H. K. Yildirim, J. Ma, and E. Matioli, IEEE Trans. Power Electron. 36(2), 1269–1273 (2021).

- <sup>3</sup>Z. Bandić, P. Bridger, E. Piquette, T. McGill, R. Vaudo, V. Phanse, and J. Redwing, Appl. Phys. Lett. 74(9), 1266–1268 (1999).

- <sup>4</sup>B. Gelmont, K. Kim, and M. Shur, J. Appl. Phys. 74(3), 1818–1821 (1993).

- <sup>5</sup>V. Kumar, W. Lu, R. Schwindt, A. Kuliev, G. Simin, J. Yang, M. A. Khan, and I. Adesida, IEEE Electron Device Lett. **23**(8), 455–457 (2002).

- <sup>6</sup>U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, Proc. IEEE **96**(2), 287–305 (2008).

- <sup>7</sup>T. Li, M. Mastro, and A. Dadgar, *III-V Compound Semiconductors: Integration with Silicon-Based Microelectronics* (CRC Press, 2010).

- <sup>8</sup>A. Dadgar, J. Bläsing, A. Diez, A. Alam, M. Heuken, and A. Krost, Jpn. J. Appl. Phys., Part 2 **39**, L1183–L1185 (2000).

- <sup>9</sup>J. Cheng, X. Yang, L. Sang, L. Guo, A. Hu, F. Xu, N. Tang, X. Wang, and B. Shen, Appl. Phys. Lett. **106**(14), 142106 (2015).

- <sup>10</sup>Y. Zhou, R. Ramaneti, J. Anaya, S. Korneychuk, J. Derluyn, H. Sun, J. Pomeroy, J. Verbeeck, K. Haenen, and M. Kuball, Appl. Phys. Lett. **111**(4), 041901 (2017).

- <sup>11</sup>Y. Feng, X. Yang, Z. Zhang, D. Kang, J. Zhang, K. Liu, X. Li, J. Shen, F. Liu, and T. Wang, Adv. Funct. Mater. 29(42), 1905056 (2019).

- <sup>12</sup>E. Feltin, B. Beaumont, M. Laügt, P. de Mierry, P. Vennéguès, H. Lahrèche, M. Leroux, and P. Gibart, Appl. Phys. Lett. **79**(20), 3230–3232 (2001).

- <sup>13</sup>S. Raghavan, X. Weng, E. Dickey, and J. M. Redwing, Appl. Phys. Lett. 88(4), 041904 (2006).

- <sup>14</sup>D. Zhao, D. Zhao, D. Jiang, Z. Liu, J. Zhu, P. Chen, W. Liu, X. Li, and M. Shi, J. Semicond. **36**(6), 063003 (2015).

- <sup>15</sup>D. Zhao and D. Zhao, J. Semicond. **39**(3), 033006 (2018).

- <sup>16</sup>S. Choi, E. Heller, D. Dorsey, R. Vetury, and S. Graham, J. Appl. Phys. 113(9), 093510 (2013).

- <sup>17</sup>X. Wang, W. Peng, R. Yu, H. Zou, Y. Dai, Y. Zi, C. Wu, S. Li, and Z. L. Wang, Nano Lett. **17**(6), 3718–3724 (2017).

- <sup>18</sup>Y. Zhou, J. Anaya, J. Pomeroy, H. Sun, X. Gu, A. Xie, E. Beam, M. Becker, T. A. Grotjohn, C. Lee, and M. Kuball, ACS Appl. Mater. Interfaces 9(39), 34416–34422 (2017).

- <sup>19</sup>M. Kuball and J. W. Pomeroy, IEEE Trans. Device Mater. Reliab. 16(4), 667–684 (2016).

- <sup>20</sup>K. H. Lee, S. Bao, L. Zhang, D. Kohen, E. Fitzgerald, and C. S. Tan, Appl. Phys. Express 9(8), 086501 (2016).

- <sup>21</sup>J. W. Chung, J.-k. Lee, E. L. Piner, and T. Palacios, IEEE Electron Device Lett. 30(10), 1015–1017 (2009).

- <sup>22</sup>C. Xiong, W. Pernice, K. K. Ryu, C. Schuck, K. Y. Fong, T. Palacios, and H. X. Tang, Opt. Express **19**(11), 10462–10470 (2011).

- <sup>23</sup>J. Liang, Y. Zhou, S. Masuya, F. Gucmann, M. Singh, J. Pomeroy, S. Kim, M. Kuball, M. Kasu, and N. Shigekawa, Diamond Relat. Mater. **93**, 187–192 (2019).

- <sup>24</sup>J. Liang, A. Kobayashi, Y. Shimizu, Y. Ohno, S. W. Kim, K. Koyama, M. Kasu, Y. Nagai, and N. Shigekawa, Adv. Mater. **33**(43), 2104564 (2021).

- <sup>25</sup>J. Liang, S. Nishida, T. Hayashi, M. Arai, and N. Shigekawa, Appl. Phys. Lett. 105(15), 151607 (2014).

- <sup>26</sup>F. Mu, Y. Wang, R. He, and T. Suga, Materialia 3, 12–14 (2018).

- 27Y. He, W. Jie, T. Wang, Y. Xu, Y. Zhou, Y. Zaman, and G. Zha, J. Cryst. Growth 402, 15–21 (2014).

- <sup>28</sup>Y. He, W. Jie, Y. Xu, Y. Wang, Y. Zhou, H. Liu, T. Wang, and G. Zha, Scr. Mater. 82, 17–20 (2014).

- <sup>29</sup>D. Liu, D. Cherns, S. Johns, Y. Zhou, J. Liu, W.-Y. Chen, I. Griffiths, C. Karthik, M. Li, M. Kuball, J. Kane, and W. Windes, Carbon 173, 215–231 (2021).

- <sup>30</sup>Y. Zhou, S. Zhou, P. Ying, Q. Zhao, Y. Xie, M. Gong, P. Jiang, H. Cai, B. Chen, S. Tongay, J. Zhang, W. Jie, T. Wang, P. Tan, D. Liu, and M. Kuball, J. Phys. Chem. Lett. **13**(17), 3831–3839 (2022).

- <sup>31</sup>J. Zhang, Y. Zhou, P. Ying, H. Sun, J. Zhou, T. Wang, W. Jie, and M. Kuball, Nanotechnology **31**(16), 165706 (2020).

- <sup>32</sup>B. Zou, Y. Zhou, X. Zhang, M. Zhang, K. Liu, M. Gong, and H. Sun, ACS Appl. Nano Mater. 3(10), 10543–10550 (2020).

- <sup>33</sup>E. Mercado, Y. Zhou, Y. Xie, Q. Zhao, H. Cai, B. Chen, W. Jie, S. Tongay, T. Wang, and M. Kuball, ACS Omega 4(19), 18002–18010 (2019).

- <sup>34</sup>L. Zhang, X. Lou, D. Wang, Y. Zhou, Y. Yang, M. Kuball, M. A. Carpenter, and X. Ren, Phys. Rev. Appl. 8(5), 054018 (2017).

- <sup>35</sup>H. Takagi, K. Kikuchi, R. Maeda, T. Chung, and T. Suga, Appl. Phys. Lett. **68**(16), 2222-2224 (1996).

- <sup>36</sup>M. Howlader, T. Watanabe, and T. Suga, J. Vac. Sci. Technol. B **19**(6), 2114–2118 (2001).

- <sup>37</sup>H. Harima, J. Phys.: Condens. Matter 14(38), R967 (2002).

- <sup>38</sup>D. Zhao, S. Xu, M. Xie, S. Tong, and H. Yang, Appl. Phys. Lett. 83(4), 677–679 (2003).

- <sup>39</sup>S. Tripathy, S. Chua, P. Chen, and Z. Miao, J. Appl. Phys. **92**(7), 3503–3510 (2002).

- <sup>40</sup>S. Hsu, B. Pong, W. Li, T. E. Beechem III, S. Graham, and C. Liu, Appl. Phys. Lett. **91**(25), 251114 (2007).

- <sup>41</sup>F. Demangeot, J. Frandon, M. Renucci, O. Briot, B. Gil, and R.-L. Aulombard, MRS Internet J. Nitride Semicond. Res. **1**, 23 (1996).

- <sup>42</sup>J. Chen and I. D. Wolf, Semicond. Sci. Technol. 18(4), 261 (2003).

- <sup>43</sup>W. Rieger, T. Metzger, H. Angerer, R. Dimitrov, O. Ambacher, and M. Stutzmann, Appl. Phys. Lett. 68(7), 970–972 (1996).

- <sup>44</sup>J. Zhang, X. Yang, Y. Feng, Y. Li, M. Wang, J. Shen, L. Wei, D. Liu, S. Wu, and Z. Cai, Phys. Rev. Mater. 4(7), 073402 (2020).

- <sup>45</sup>J. Liang, L. Chai, S. Nishida, M. Morimoto, and N. Shigekawa, Jpn. J. Appl. Phys., Part 1 54(3), 030211 (2015).

- <sup>46</sup>J. Liang, S. Masuya, M. Kasu, and N. Shigekawa, Appl. Phys. Lett. **110**(11), 111603 (2017).

- <sup>47</sup>R. Graupner, Q. Ye, T. Warwick, and E. Bourret-Courchesne, J. Cryst. Growth 217(1-2), 55–64 (2000).